# Power delivery network in the advanced packaging

### Jaemyung Lim

iSoC Lab, School of Electrical Engineering, Hanyang University, Seoul, South Korea

#### 1. Objectives

- >Because of advances in machine learning and AI, demands on highperformance processing units are highly increased.

- >On the other hand, development of the semiconductor technology has been gradually slowed down.

- >The scaling of embedded memories in a processing unit is not as efficient as that of logic gates in technology development, and static power consumption of it is significantly increased.

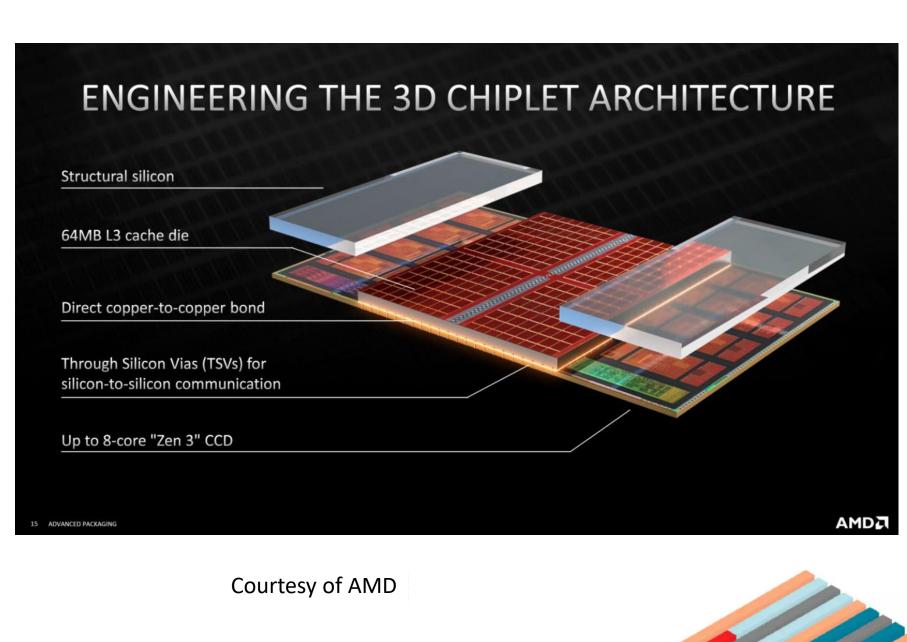

- Therefore, 3-D chiplet architecture with different technology for each IPs are recently studied.

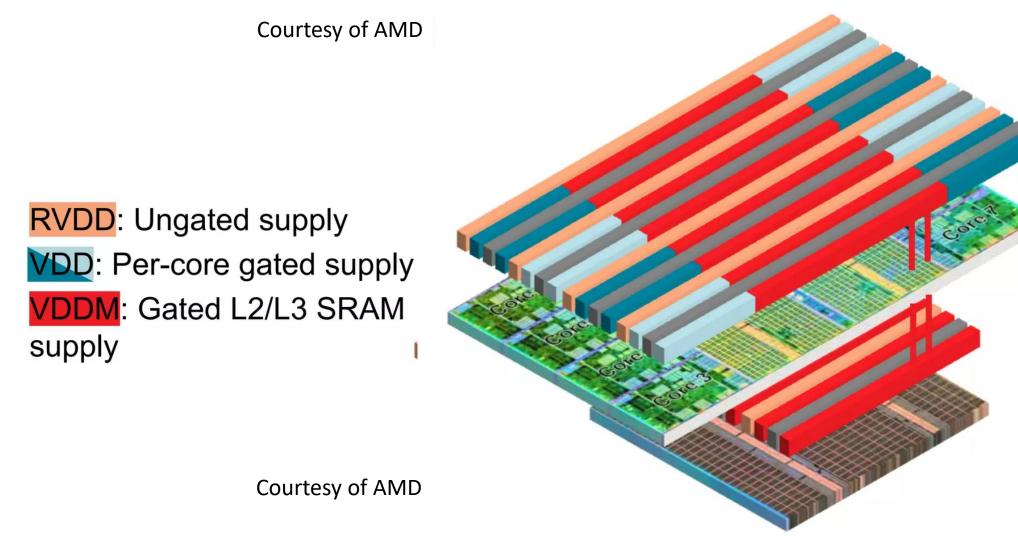

- >In a 3-D chiplet, where more than two chips are stacked and share a power delivery network (PDN), analyzing the PDN becomes significantly complicated.

- >We are developing equivalent model of on-chip + package PDN for efficient and accurate simulation

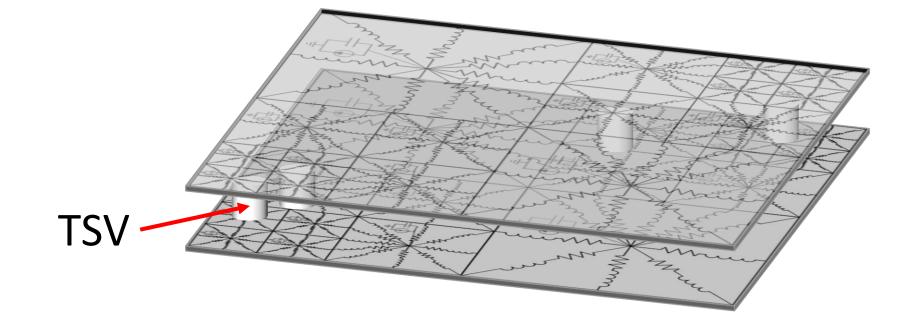

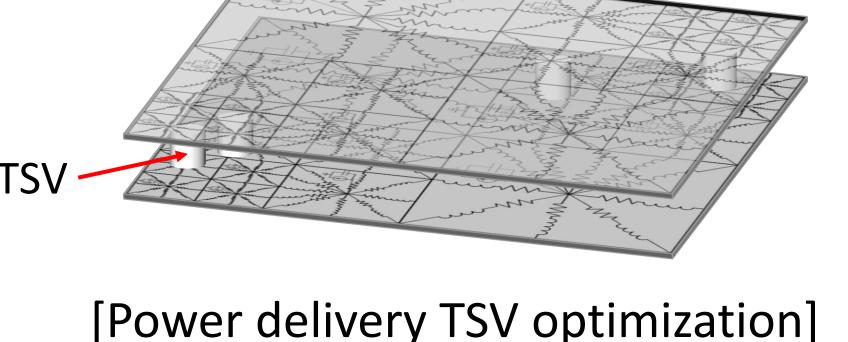

## 2. Power delivery network (PDN) modeling and through silicon via (TSV) optimization

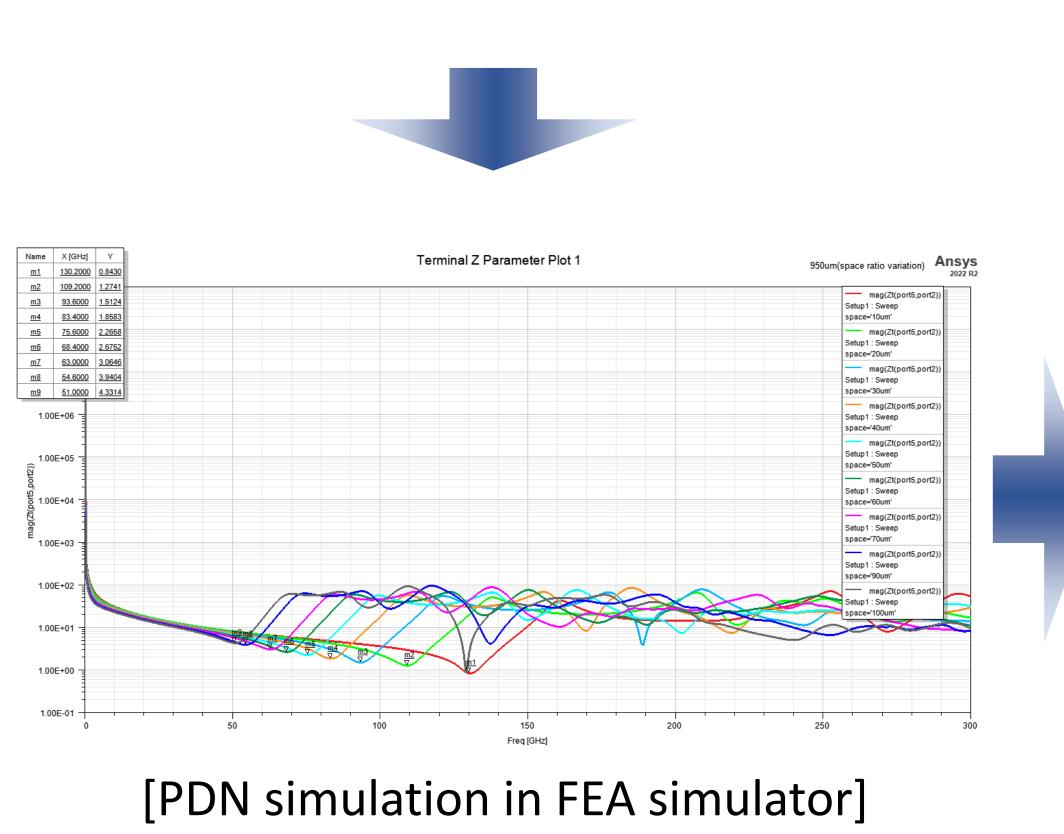

➤ Based on the S-parameter, we calculate Z-parameter and corresponding RLC values.

capacitance.

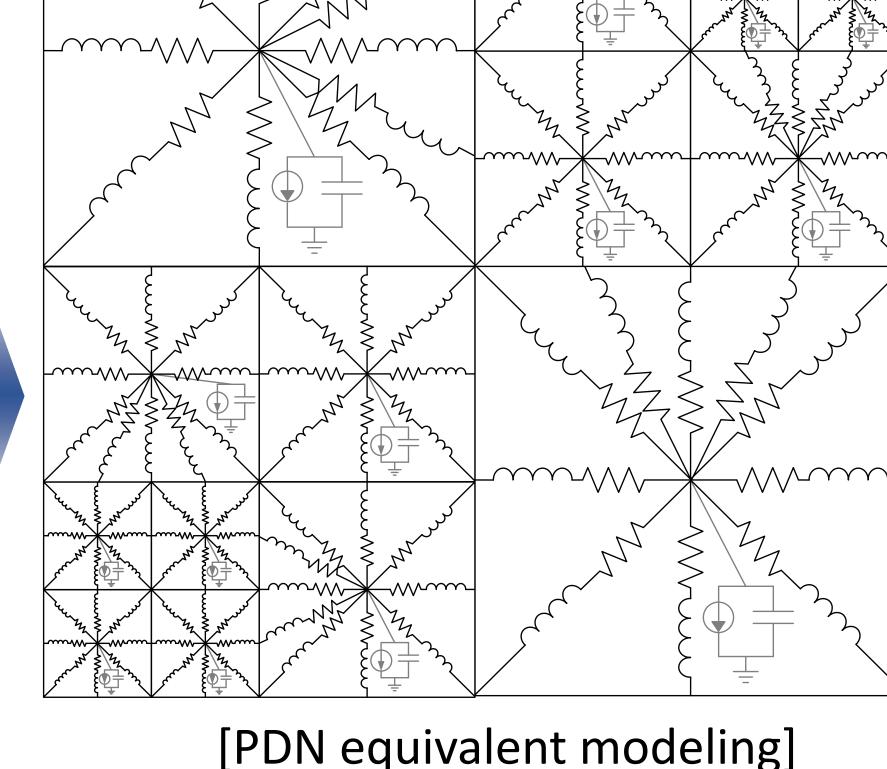

To reduce the complexity of the power delivery network (PDN), we use small for areas requiring detailed analysis, and larger "tiles" for other areas.

>We use the finite element analysis

(FEA) simulator ANSYS to calculate

inductance, as well as resistance and

>We optimize the number and placement of TSVs for power delivery based on the analysis of the PDN.

#### 3. Collaboration with United states

- > We are plan to collaborate with Professor Degertekin in GeorgiaTech about brain cancer immunotherapy.

- PennState > We are plan to collaborate with Professor Kiani in PennState university about packaging under wireless power transmission environment.